Difference between revisions of "Rock3/CM/CM3/pinout"

RadxaYuntian (Talk | contribs) (→Pinout Change History) |

RadxaYuntian (Talk | contribs) (→Pinout Change History) |

||

| Line 2,755: | Line 2,755: | ||

V1.31 pinout changes from V1.3 | V1.31 pinout changes from V1.3 | ||

| − | * Swap Pin 37, Pin 14, Pin | + | * Swap Pin 37, Pin 14, Pin 34 signal |

V1.32 pinout changes from V1.31 | V1.32 pinout changes from V1.31 | ||

Revision as of 08:21, 3 April 2023

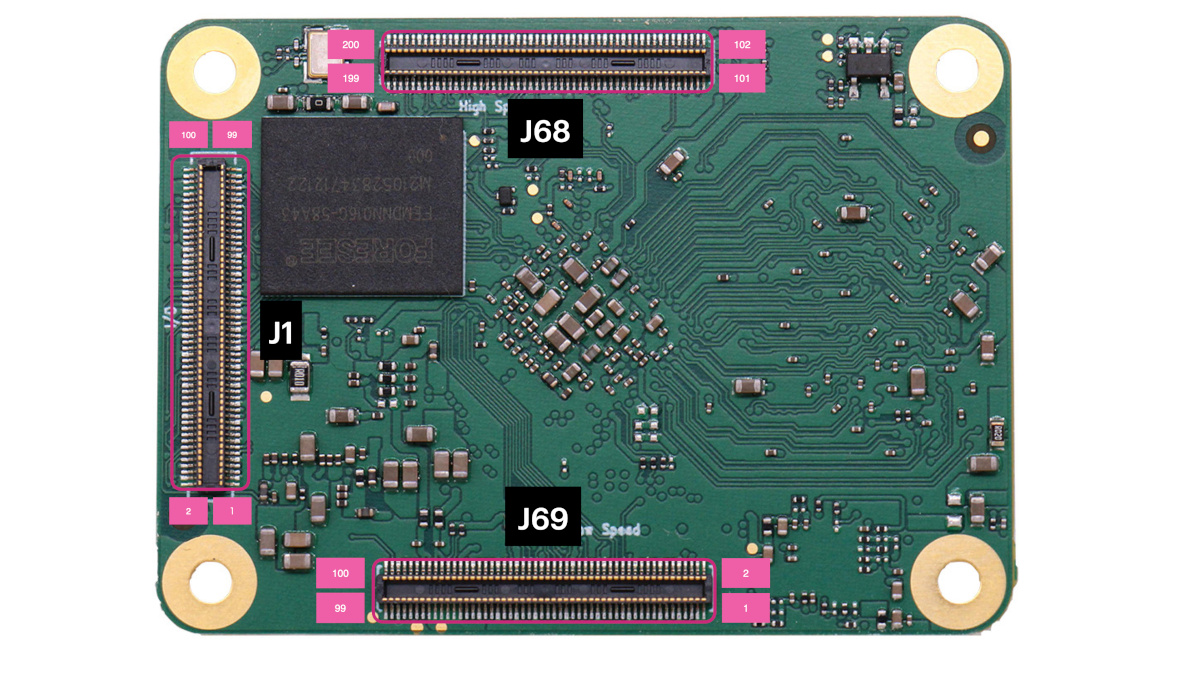

ROCK 3 > Compute Module > CM3 > CM3 Pinout

CM3 Revision v1.3

Download radxa_cm3_v1.3_pinout.xlsx

| Connector 1 (J69) | |||||||

|---|---|---|---|---|---|---|---|

| Pin Number | Function CM3 IO Board | Function 0 | Function 1 | Function 2 | Function 3 | Function 4 | Function 5 |

| 1 | GND | ||||||

| 2 | GND | ||||||

| 3 | PHY1_MDI3+ | ||||||

| 4 | PHY1_MDI1+ | ||||||

| 5 | PHY1_MDI3- | ||||||

| 6 | PHY1_MDI1- | ||||||

| 7 | GND | ||||||

| 8 | GND | ||||||

| 9 | PHY1_MDI2- | ||||||

| 10 | PHY1_MDI0- | ||||||

| 11 | PHY1_MDI2+ | ||||||

| 12 | PHY1_MDI0+ | ||||||

| 13 | GND | ||||||

| 14 | GND | ||||||

| 15 | PHY1_LED2_Y | ||||||

| 16 | NC | ||||||

| 17 | PHY1_LED1_G | ||||||

| 18 | NC | ||||||

| 19 | PHY1_LED0_Y1 | ||||||

| 20 | EEPROM_NWP | ||||||

| 21 | PI_NLED_ACTIVITY | GPIO4_A4 | CIF_D14 | EBC_SDDO14 | GMAC1_TXD0_M1 | UART9_TX_M2 | I2S2_LRCK_TX_M1 |

| 22 | GND | ||||||

| 23 | GND | ||||||

| 24 | PWM3_IR | GPIO0_C2 | PWM3_IR | EDP_HPDIN_M1 | MCU_JTAG_TMS | ||

| 25 | I2S1_SDO0_M1 | GPIO3_D1 | CIF_D3 | EBC_SDDO3 | SDMMC2_D3_M0 | I2S1_SDO0_M1 | VOP_BT656_D3_M1 |

| 26 | I2S1_LRCK_TX_M1 | GPIO3_D0 | CIF_D2 | EBC_SDDO2 | SDMMC2_D2_M0 | I2S1_LRCK_TX_M1 | VOP_BT656_D2_M1 |

| 27 | I2S1_SDI0_M1 | GPIO3_D2 | CIF_D4 | EBC_SDDO4 | SDMMC2_CMD_M0 | I2S1_SDI0_M1 | VOP_BT656_D4_M1 |

| 28 | SPI0_CSO_MO | GPIO0_C6 | PWM7_IR | SPI0_CS0_M0 | |||

| 29 | I2S1_LRCK_RX_M1 | GPIO4_A7 | CAM_CLKOUT0 | EBC_SDCE1 | GMAC1_RXD0_M1 | SPI3_CS1_M0 | I2S1_LRCK_RX_M1 |

| 30 | SPI0_MISO_MO | GPIO0_C5 | PWM6 | SPI0_MISO_M0 | |||

| 31 | PWM11 | GPIO4_C0 | CIF_CLKOUT | EBC_GDCLK | PWM11_IR_M1 | ||

| 32 | GND | ||||||

| 33 | GND | ||||||

| 34 | I2S1_SDO2_M1 | GPIO4_B1 | ISP_PRELIGHT_TRIG | EBC_SDCE3 | GMAC1_RXDV_CRS_M1 | I2S1_SDO2_M1 | |

| 35 | I2C2_SCL_M1 | GPIO4_B5 | I2C2_SCL_M1 | EBC_SDSHR | I2S1_SDO3_M1 | ||

| 36 | I2C2_SDA_M1 | GPIO4_B4 | I2C2_SDA_M1 | EBC_GDSP | ISP_FLASH_TRIGIN | VOP_BT656_CLK_M1 | |

| 37 | SARADC_IN3 | SARADC_VIN3 | |||||

| 38 | SPI3_CLK_M0 | GPIO4_B3 | I2C4_SCL_M0 | EBC_GDOE | ETH1_REFCLKO_25M_M1 | SPI3_CLK_M0 | I2S2_SDO_M1 |

| 39 | SPI3_CSO_M0 | GPIO4_A6 | ISP_FLASHTRIGOUT | EBC_SDCE0 | GMAC1_TXEN_M1 | SPI3_CS0_M0 | I2S1_SCLK_RX_M1 |

| 40 | SPI3_MISO_M0 | GPIO4_B0 | CAM_CLKOUT1 | EBC_SDCE2 | GMAC1_RXD1_M1 | SPI3_MISO_M0 | I2S1_SDO1_M1 |

| 41 | I2S1_MCLK_M1 | GPIO3_C6 | CIF_D0 | EBC_SDDO0 | SDMMC2_D0_M0 | I2S1_MCLK_M1 | VOP_BT656_D0_M1 |

| 42 | GND | ||||||

| 43 | GND | ||||||

| 44 | SPI3_MOSI_M0 | GPIO4_B2 | I2C4_SDA_M0 | EBC_VCOM | GMAC1_RXER_M1 | SPI3_MOSI_M0 | I2S2_SDI_M1 |

| 45 | I2S1_SDI1_M1 | GPIO3_D3 | CIF_D5 | EBC_SDDO5 | SDMMC2_CLK_M0 | I2S1_SDI1_M1 | VOP_BT656_D5_M1 |

| 46 | PMW4 | GPIO0_C3 | PWM4 | VOP_PWM_M0 | MCU_JTAG_TRSTn | ||

| 47 | I2S1_SDI2_M1 | GPIO3_D4 | CIF_D6 | EBC_SDDO6 | SDMMC2_DET_M0 | I2S1_SDI2_M1 | VOP_BT656_D6_M1 |

| 48 | PMW0_M0 | GPIO0_B7 | PWM0_M0 | CPUAVS | |||

| 49 | I2S1_SCLK_TX_M1 | GPIO3_C7 | CIF_D1 | EBC_SDDO1 | SDMMC2_D1_M0 | I2S1_SCLK_TX_M1 | VOP_BT656_D1_M1 |

| 50 | PMW0_M1 | GPIO0_C7 | HDMITX_CEC_M1 | PWM0_M1 | UART0_CTSn | ||

| 51 | UART2_RX | GPIO0_D0 | UART2_RX_M0 | ||||

| 52 | GND | ||||||

| 53 | GND | ||||||

| 54 | I2S1_SDI3_M1 | GPIO3_D5 | CIF_D7 | EBC_SDDO7 | SDMMC2_PWREN_M0 | I2S1_SDI3_M1 | VOP_BT656_D7_M1 |

| 55 | UART2_TX | GPIO0_D1 | UART2_TX_M0 | ||||

| 56 | I2C2_SCL_MO | GPIO0_B5 | I2C2_SCL_M0 | SPI0_CLK_M0 | PCIE20_WAKEn_M0 | PWM1_M1 | |

| 57 | SDMMC0_CLK | GPIO2_A2 | SDMMC0_CLK | TEST_CLKOUT | UART5_TX_M0 | ||

| 58 | I2C2_SDA_MO | GPIO0_B6 | I2C2_SDA_M0 | SPI0_MOSI_M0 | PCIE20_PERSTn_M0 | PWM2_M1 | |

| 59 | GND | ||||||

| 60 | GND | ||||||

| 61 | SDMMC0_D3 | GPIO2_A0 | SDMMC0_D3 | ARM_JTAG_TMS | UART5_RTSn_M0 | ||

| 62 | SDMMC0_CMD | GPIO2_A1 | SDMMC0_CMD | PWM10_M1 | UART5_RX_M0 | ||

| 63 | SDMMC0_D0 | GPIO1_D5 | SDMMC0_D0 | UART2_TX_M1 | UART6_TX_M1 | PWM8_M1 | |

| 64 | NC | ||||||

| 65 | GND | ||||||

| 66 | GND | ||||||

| 67 | SDMMC0_D1 | GPIO1_D6 | SDMMC0_D1 | UART2_RX_M1 | UART6_RX_M1 | PWM9_M1 | |

| 68 | NC | ||||||

| 69 | SDMMC0_D2 | GPIO1_D7 | SDMMC0_D2 | ARM_JTAG_TCK | UART5_CTSn_M0 | ||

| 70 | NC | ||||||

| 71 | GND | ||||||

| 72 | NC | ||||||

| 73 | NC | ||||||

| 74 | GND | ||||||

| 75 | SDMMC_PWREN | GPIO0_A5 | SDMMC0_PWREN | SATA_MP_SWITCH | PCIE20_CLKREQn_M0 | ||

| 76 | SDMMC0_DET_L | GPIO0_A4 | SDMMC0_DET | SATA_CP_DET | |||

| 77 | +5V_INPUT | ||||||

| 78 | GPIO_VREF | ||||||

| 79 | +5V_INPUT | ||||||

| 80 | I2C0_SCL_PMIC | GPIO0_B1 | I2C0_SCL | ||||

| 81 | +5V_INPUT | ||||||

| 82 | I2C0_SDA_PMIC | GPIO0_B2 | I2C0_SDA | ||||

| 83 | +5V_INPUT | ||||||

| 84 | +3V3 | ||||||

| 85 | +5V_INPUT | ||||||

| 86 | +3V3 | ||||||

| 87 | +5V_INPUT | ||||||

| 88 | +1V8 | ||||||

| 89 | WL_NDIS | GPIO4_B6 | CIF_HREF | EBC_SDLE | GMAC1_MDC_M1 | UART1_RTSn_M1 | I2S2_MCLK_M1 |

| 90 | +1V8 | ||||||

| 91 | BT_NDIS | GPIO4_A5 | CIF_D15 | EBC_SDDO15 | GMAC1_TXD1_M1 | UART9_RX_M2 | I2S2_LRCK_RX_M1 |

| 92 | PMIC_SLEEP_H | GPIO0_A2 | PMIC_SLEEP | TSADC_SHUT_M1 | |||

| 93 | NC | ||||||

| 94 | NC | ||||||

| 95 | NPWR_LED | GPIO4_B7 | CIF_VSYNC | EBC_SDOE | GMAC1_MDIO_M1 | I2S2_SCLK_TX_M1 | |

| 96 | NC | ||||||

| 97 | CAM_GPIO | GPIO4_C1 | CIF_CLKIN | EBC_SDCLK | GMAC1_MCLKINOUT_M1 | UART1_CTSn_M1 | I2S2_SCLK_RX_M1 |

| 98 | GND | ||||||

| 99 | PWRON_KEY | ||||||

| 100 | PMIC_RESET_KEY | ||||||

| Connector 2 (J68) | |||||||

| Pin Number | Function CM3 IO Board | Function 0 | Function 1 | Function 2 | Function 3 | Function 4 | Function 5 |

| 101 | USB_OTG0_ID | USB_OTG0_ID | |||||

| 102 | PCIE20_CLKREQN_M2 | GPIO1_B0 | I2S1_SDO1_M0 | I2S1_SDI3_M0 | PDM_SDI3_M0 | PCIE20_CLKREQn_M2 | |

| 103 | USB_OTG0_DM | USB_OTG0_DM | |||||

| 104 | NC | ||||||

| 105 | USB_OTG0_DP | USB_OTG0_DP | |||||

| 106 | NC | ||||||

| 107 | GND | ||||||

| 108 | GND | ||||||

| 109 | PCIE_NRST | GPIO1_B2 | I2S1_SDO3_M0 | I2S1_SDI1_M0 | PDM_SDI1_M0 | PCIE20_PERSTn_M2 | |

| 110 | PCIE20_REFCLKP | PCIE20_REFCLKP | |||||

| 111 | NC | ||||||

| 112 | PCIE20_REFCLKN | PCIE20_REFCLKN | |||||

| 113 | GND | ||||||

| 114 | GND | ||||||

| 115 | MIPI_CSI_RX_D0N | MIPI_CSI_RX_D0N | |||||

| 116 | PCIE20_RXP | PCIE20_RXP | SATA2_RXP | ||||

| 117 | MIPI_CSI_RX_D0P | MIPI_CSI_RX_D0P | |||||

| 118 | PCIE20_RXN | PCIE20_RXN | SATA2_RXN | ||||

| 119 | GND | ||||||

| 120 | GND | ||||||

| 121 | MIPI_CSI_RX_D1N | MIPI_CSI_RX_D1N | -- | ||||

| 122 | PCIE20_TXP | PCIE20_TXP | SATA2_TXP | ||||

| 123 | MIPI_CSI_RX_D1P | MIPI_CSI_RX_D1P | -- | ||||

| 124 | PCIE20_TXN | PCIE20_TXN | SATA2_TXN | ||||

| 125 | GND | ||||||

| 126 | GND | ||||||

| 127 | MIPI_CSI_RX_CLK0N | MIPI_CSI_RX_CLK0N | |||||

| 128 | MIPI_CSI_RX_D2N | MIPI_CSI_RX_D2N | |||||

| 129 | MIPI_CSI_RX_CLK0P | MIPI_CSI_RX_CLK0P | |||||

| 130 | MIPI_CSI_RX_D2P | MIPI_CSI_RX_D2P | |||||

| 131 | GND | ||||||

| 132 | GND | ||||||

| 133 | NC | ||||||

| 134 | MIPI_CSI_RX_D3N | MIPI_CSI_RX_D3N | |||||

| 135 | NC | ||||||

| 136 | MIPI_CSI_RX_D3P | MIPI_CSI_RX_D3P | |||||

| 137 | GND | ||||||

| 138 | GND | ||||||

| 139 | NC | ||||||

| 140 | MIPI_CSI_RX_CLK1N | MIPI_CSI_RX_CLK1N | |||||

| 141 | NC | ||||||

| 142 | MIPI_CSI_RX_CLK1P | MIPI_CSI_RX_CLK1P | |||||

| 143 | NC | ||||||

| 144 | GND | ||||||

| 145 | NC | ||||||

| 146 | NC | ||||||

| 147 | NC | ||||||

| 148 | NC | ||||||

| 149 | NC | ||||||

| 150 | GND | ||||||

| 151 | HDMI_TX_CEC_PORT | GPIO4_D1 | HDMITX_CEC_M0 | SPI3_CS1_M1 | |||

| 152 | NC | ||||||

| 153 | HDMI_TX_HPD_PORT | HDMI_TX_HPDIN | |||||

| 154 | NC | ||||||

| 155 | GND | ||||||

| 156 | GND | ||||||

| 157 | MIPI_DSI_TX0_D0N/LVDS_TX0_D0N | MIPI_DSI_TX0_D0N | LVDS_TX0_D0N | ||||

| 158 | NC | ||||||

| 159 | MIPI_DSI_TX0_D0P/LVDS_TX0_D0P | MIPI_DSI_TX0_D0P | LVDS_TX0_D0P | ||||

| 160 | NC | ||||||

| 161 | GND | ||||||

| 162 | GND | ||||||

| 163 | MIPI_DSI_TX0_D1N/LVDS_TX0_D1N | MIPI_DSI_TX0_D1N | LVDS_TX0_D1N | ||||

| 164 | NC | ||||||

| 165 | MIPI_DSI_TX0_D1P/LVDS_TX0_D1P | MIPI_DSI_TX0_D1P | LVDS_TX0_D1P | ||||

| 166 | NC | ||||||

| 167 | GND | ||||||

| 168 | GND | ||||||

| 169 | MIPI_DSI_TX0_CLKN/LVDS_TX0_CLKN | MIPI_DSI_TX0_CLKN | LVDS_TX0_CLKN | ||||

| 170 | HDMI_TX2P_PORT | HDMI_TX_D2P | -- | ||||

| 171 | MIPI_DSI_TX0_CLKP/LVDS_TX0_CLKP | MIPI_DSI_TX0_CLKP | LVDS_TX0_CLKP | ||||

| 172 | HDMI_TX2N_PORT | HDMI_TX_D2N | |||||

| 173 | GND | ||||||

| 174 | GND | ||||||

| 175 | MIPI_DSI_TX1_D0N | MIPI_DSI_TX1_D0N | |||||

| 176 | HDMI_TX1P_PORT | HDMI_TX_D1P | |||||

| 177 | MIPI_DSI_TX1_D0P | MIPI_DSI_TX1_D0P | |||||

| 178 | HDMI_TX1N_PORT | HDMI_TX_D1N | |||||

| 179 | GND | ||||||

| 180 | GND | ||||||

| 181 | MIPI_DSI_TX1_D1N | MIPI_DSI_TX1_D1N | |||||

| 182 | HDMI_TX0P_PORT | HDMI_TX_D0P | |||||

| 183 | MIPI_DSI_TX1_D1P | MIPI_DSI_TX1_D1P | |||||

| 184 | HDMI_TX0N_PORT | HDMI_TX_D0N | |||||

| 185 | GND | ||||||

| 186 | GND | ||||||

| 187 | MIPI_DSI_TX1_CLKN | MIPI_DSI_TX1_CLKN | |||||

| 188 | HDMI_TXCLKP_PORT | HDMI_TX_CLKP | |||||

| 189 | MIPI_DSI_TX1_CLKP | MIPI_DSI_TX1_CLKP | |||||

| 190 | HDMI_TXCLKN_PORT | HDMI_TX_CLKN | |||||

| 191 | GND | ||||||

| 192 | GND | ||||||

| 193 | MIPI_DSI_TX1_D2N | MIPI_DSI_TX1_D2N | |||||

| 194 | MIPI_DSI_TX1_D3N | MIPI_DSI_TX1_D3N | |||||

| 195 | MIPI_DSI_TX1_D2P | MIPI_DSI_TX1_D2P | |||||

| 196 | MIPI_DSI_TX1_D3P | MIPI_DSI_TX1_D3P | |||||

| 197 | GND | ||||||

| 198 | GND | ||||||

| 199 | HDMI_TXDDC_SDA_PORT | GPIO4_D0 | HDMITX_SDA | I2C5_SDA_M1 | |||

| 200 | HDMI_TXDDC_SCL_PORT | GPIO4_C7 | HDMITX_SCL | I2C5_SCL_M1 | |||

| Connector 3 (J1) | |||||||

| Pin Number | Function CM3 IO Board | Function 0 | Function 1 | Function 2 | Function 3 | Function 4 | Function 5 |

| 1 | GND | ||||||

| 2 | GND | ||||||

| 3 | MIPI_DSI_TX0_D2N/LVDS_TX0_D2N | MIPI_DSI_TX0_D2N | LVDS_TX0_D2N | ||||

| 4 | GPIO3_A1 | GPIO3_A1 | VOP_BT1120_D0 | SPI1_CS0_M1 | SDMMC2_D0_M1 | -- | |

| 5 | MIPI_DSI_TX0_D2P/LVDS_TX0_D2P | MIPI_DSI_TX0_D2P | LVDS_TX0_D2P | ||||

| 6 | GPIO3_B4 | GPIO3_B4 | VOP_BT1120_D10 | GMAC1_RXER_M0 | I2C5_SDA_M0 | PDM_SDI1_M2 | |

| 7 | GND | ||||||

| 8 | GPIO3_C1 | GPIO3_C1 | VOP_BT1120_D13 | SPI1_MOSI_M1 | PCIE20_PERSTn_M1 | I2S1_SDO2_M2 | |

| 9 | MIPI_DSI_TX0_D3N/LVDS_TX0_D3N | MIPI_DSI_TX0_D3N | LVDS_TX0_D3N | ||||

| 10 | GPIO3_C2 | GPIO3_C2 | VOP_BT1120_D14 | SPI1_MISO_M1 | UART5_TX_M1 | I2S1_SDO3_M2 | |

| 11 | MIPI_DSI_TX0_D3P/LVDS_TX0_D3P | MIPI_DSI_TX0_D3P | LVDS_TX0_D3P | ||||

| 12 | GPIO3_C3 | GPIO3_C3 | VOP_BT1120_D15 | SPI1_CLK_M1 | UART5_RX_M1 | I2S1_SCLK_RX_M2 | |

| 13 | GND | ||||||

| 14 | PCIE_PWREN_H | GPIO0_D3 | |||||

| 15 | EDP_TX_D0P | EDP_TX_D0P | |||||

| 16 | NC | ||||||

| 17 | EDP_TX_D0N | EDP_TX_D0N | |||||

| 18 | GPIO_D5 | GPIO0_D5 | |||||

| 19 | GND | ||||||

| 20 | GPIO_D6 | GPIO0_D6 | |||||

| 21 | EDP_TX_D1P | EDP_TX_D1P | |||||

| 22 | GND | ||||||

| 23 | EDP_TX_D1N | EDP_TX_D1N | |||||

| 24 | GPIO2_C6 | GPIO2_C6 | CLK32K_OUT1 | UART8_RX_M0 | SPI1_CS1_M0 | ||

| 25 | GND | ||||||

| 26 | SARADC_VIN0_KEY/RECOVERY | SARADC_VIN0 | |||||

| 27 | EDP_TX_D2P | EDP_TX_D2P | |||||

| 28 | SARADC_VIN1_HW_ID | SARADC_VIN1 | |||||

| 29 | EDP_TX_D2N | EDP_TX_D2N | |||||

| 30 | SARADC_VIN2_HP_HOOK | ||||||

| 31 | GND | ||||||

| 32 | GND | ||||||

| 33 | EDP_TX_D3P | EDP_TX_D3P | |||||

| 34 | 4G_DISABLE | GPIO4_C5 | PWM12_M1 | SPI3_MISO_M1 | SATA1_ACT_LED | UART9_TX_M1 | I2S3_SDO_M1 |

| 35 | EDP_TX_D3N | EDP_TX_D3N | |||||

| 36 | HP_DET_L | GPIO4_C6 | PWM13_M1 | SPI3_CS0_M1 | SATA0_ACT_LED | UART9_RX_M1 | I2S3_SDI_M1 |

| 37 | GND | ||||||

| 38 | PDM_SDI2_M0_ADC | GPIO1_B1 | I2S1_SDO2_M0 | I2S1_SDI2_M0 | PDM_SDI2_M0 | PCIE20_WAKEn_M2 | |

| 39 | EDP_TX_AUXP | EDP_TX_AUXP | |||||

| 40 | PDM_CLK1_M0 | GPIO1_A4 | I2S1_SCLK_RX_M0 | UART4_RX_M0 | PDM_CLK1_M0 | SPDIF_TX_M0 | |

| 41 | EDP_TX_AUXN | EDP_TX_AUXN | |||||

| 42 | GND | ||||||

| 43 | GND | ||||||

| 44 | I2C3_SCL_ACODEC | GPIO1_A1 | I2C3_SCL_M0 | UART3_TX_M0 | AUDIOPWM_LOUT_N | ||

| 45 | USB3_HOST1_DP | USB_HOST1_DP | -- | ||||

| 46 | I2C3_SDA_ACODEC | GPIO1_A0 | I2C3_SDA_M0 | UART3_RX_M0 | AUDIOPWM_LOUT_P | ||

| 47 | USB3_HOST1_DM | USB_HOST1_DM | |||||

| 48 | GND | ||||||

| 49 | GND | ||||||

| 50 | HPL_OUT | ||||||

| 51 | USB3_HOST1_SSTXP | USB3_HOST1_SSTXP | SATA1_TXP | ||||

| 52 | HP_SNS | ||||||

| 53 | USB3_HOST1_SSTXN | USB3_HOST1_SSTXN | SATA1_TXN | ||||

| 54 | HPR_OUT | ||||||

| 55 | GND | ||||||

| 56 | GND | ||||||

| 57 | USB3_HOST1_SSRXP | USB3_HOST1_SSRXP | SATA1_RXP | ||||

| 58 | SPKN_OUT | ||||||

| 59 | USB3_HOST1_SSRXN | USB3_HOST1_SSRXN | SATA1_RXN | ||||

| 60 | SPKP_OUT | ||||||

| 61 | GND | ||||||

| 62 | GND | ||||||

| 63 | USB2_HOST2_DP | USB_HOST2_DP | |||||

| 64 | MIC1_IN | ||||||

| 65 | USB2_HOST2_DM | USB_HOST2_DM | |||||

| 66 | MIC2_IN | ||||||

| 67 | GND | ||||||

| 68 | GND | ||||||

| 69 | USB2_HOST3_DP | USB_HOST3_DP | |||||

| 70 | SPDIF_TX_M2 | GPIO4_C4 | EDP_HPDIN_M0 | SPDIF_TX_M2 | SATA2_ACT_LED | I2S3_LRCK_M1 | |

| 71 | USB2_HOST3_DM | USB_HOST3_DM | |||||

| 72 | GND | ||||||

| 73 | GND | ||||||

| 74 | WIFI_PWREN | GPIO0_A0 | REFCLK_OUT | ||||

| 75 | PDM_CLK0_M1 | GPIO3_D6 | CIF_D8 | EBC_SDDO8 | GMAC1_TXD2_M1 | UART1_TX_M1 | PDM_CLK0_M1 |

| 76 | GND | ||||||

| 77 | PDM_SDIO_M1 | GPIO3_D7 | CIF_D9 | EBC_SDDO9 | GMAC1_TXD3_M1 | UART1_RX_M1 | PDM_SDI0_M1 |

| 78 | VCC_BAT- | ||||||

| 79 | PDM_CLK1_M1 | GPIO4_A0 | CIF_D10 | EBC_SDDO10 | GMAC1_TXCLK_M1 | PDM_CLK1_M1 | |

| 80 | VCC_BAT- | ||||||

| 81 | PDM_SDI1_M1 | GPIO4_A1 | CIF_D11 | EBC_SDDO11 | GMAC1_RXD2_M1 | PDM_SDI1_M1 | |

| 82 | VCC_BAT- | ||||||

| 83 | PDM_SDI2_M1 | GPIO4_A2 | CIF_D12 | EBC_SDDO12 | GMAC1_RXD3_M1 | UART7_TX_M2 | PDM_SDI2_M1 |

| 84 | VCC_BAT+ | ||||||

| 85 | PDM_SDI3_M1 | GPIO4_A3 | CIF_D13 | EBC_SDDO13 | GMAC1_RXCLK_M1 | UART7_RX_M2 | PDM_SDI3_M1 |

| 86 | VCC_BAT+ | ||||||

| 87 | GPIO_B3 | GPIO0_B3 | I2C1_SCL | MCU_JTAG_TDO | |||

| 88 | VCC_BAT+ | ||||||

| 89 | GPIO_B4 | GPIO0_B4 | I2C1_SDA | PCIE20_BUTTONRSTn | MCU_JTAG_TCK | ||

| 90 | TS | ||||||

| 91 | NC | ||||||

| 92 | VCC_SD | ||||||

| 93 | GPIO_C1 | GPIO0_C1 | PWM2_M0 | NPUAVS | UART0_TX | MCU_JTAG_TDI | |

| 94 | USB_5V_IN | ||||||

| 95 | GPIO_C4 | GPIO0_C4 | PWM5 | SPI0_CS1_M0 | UART0_RTSn | ||

| 96 | USB_5V_IN | ||||||

| 97 | USB_OTG0_VBUSDET | USB_OTG0_VBUSDET | |||||

| 98 | USB_5V_IN | ||||||

| 99 | GND | ||||||

| 100 | GND | ||||||

Pinout Change History

V1.3 pinout changes from V1.2/V1.1:

- Pin92 on J69 was NC on V1.1/V1.2 now connects to PMIC_SLEEP_H on V1.3 for external CPU status

- Split one 4-lanes MIPI CSI to two 2-lanes MIPI CSI: move MIPI_CSI_RX_D3N/P, MIPI_CSI_RX_D4N/P from Pin133/135, Pin139/141 on V1.1/V1.2 to Pin128/130, Pin 134/136 on V1.3

V1.31 pinout changes from V1.3

- Swap Pin 37, Pin 14, Pin 34 signal

V1.32 pinout changes from V1.31

- Swap Pin 93 and Pin 26

summary as table below:

| Connector 1 (J69) | ||||

|---|---|---|---|---|

| Pin Number | CM3 Revision V1.32 | CM3 Revision V1.31 | CM3 Revision V1.3 | CM3 Revision V1.1/V1.2 |

| 37 | 4G_DISABLE | 4G_DISABLE | SARADC_IN3 | SARADC_IN3 |

| 92 | PMIC_SLEEP_H | PMIC_SLEEP_H | PMIC_SLEEP_H | NC |

| 93 | SARADC_VIN0_KEY/RECOVERY | NC | NC | NC |

| Connector 2 (J68) | ||||

| Pin Number | CM3 Revision V1.32 | CM3 Revision V1.31 | CM3 Revision V1.3 | CM3 Revision V1.1/V1.2 |

| 14 | SARADC_IN3 | SARADC_IN3 | PCIE_PWREN_H | PCIE_PWREN_H |

| 26 | NC | SARADC_VIN0_KEY/RECOVERY | SARADC_VIN0_KEY/RECOVERY | SARADC_VIN0_KEY/RECOVERY |

| 34 | PCIE_PWREN_H | PCIE_PWREN_H | 4G_DISABLE | 4G_DISABLE |

| 128 | MIPI_CSI_RX_D2N | MIPI_CSI_RX_D2N | MIPI_CSI_RX_D2N | NC |

| 130 | MIPI_CSI_RX_D2P | MIPI_CSI_RX_D2P | MIPI_CSI_RX_D2P | NC |

| 134 | MIPI_CSI_RX_D3N | MIPI_CSI_RX_D3N | MIPI_CSI_RX_D3N | NC |

| 136 | MIPI_CSI_RX_D3P | MIPI_CSI_RX_D3P | MIPI_CSI_RX_D3P | NC |

| 133 | NC | NC | NC | MIPI_CSI_RX_D2N |

| 135 | NC | NC | NC | MIPI_CSI_RX_D2P |

| 139 | NC | NC | NC | MIPI_CSI_RX_D3N |

| 141 | NC | NC | NC | MIPI_CSI_RX_D3P |